error “DownLoad elf failed” ; The error point

is finally located

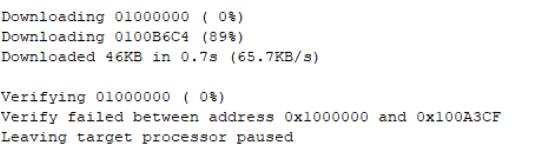

Verify failed between address 0x1000000 and 0x100A3CF

through QSYS positioning is SDRAM problem, but the program was debugging yesterday, why is there an error?

change the SDRAM connection, recompile without

confirm SDRAM pin definition again, no error, continue running without result.

remove yesterday’s new interface, no result…

no way to open the downloaded file the day before yesterday, open Quartus, direct Programmer, after passing, open Eclipse debug, success

does it need to be reactivated?Or does it have to do with the order in which the software is run?

Verify failed between address … The view has been noted

reproduced in: http://www.cnblogs.com/kongqiweiliang/p/3274226.html

nios Project: ‘m.e. ELF Process failed’ Error Running in the Process of RUN after compilation and completion of the Project cause:

1, nios2 CPU datamaster is not connected to on chinp ram, so the program cannot be downloaded on the system ram.

2. When loading SDRAM module, attention should be paid to the accuracy of its parameters, otherwise the data bus data transmission will also be affected, resulting in this problem.

3, also, in the construction of the project to choose soft core. Sopcinfo file to pay attention to the path, the general nios ii new project default last project. Sopcinfo file, it is very easy to select the file, leading to run failure.

4. There may be a problem between the sdram clock and the CPU clock.

5, PLL problem, reconfigure PLL. Turn off the Nios II IDE and recompile.

Altea

Title: Error Running Nios II Project: ‘Downloading ELF Process failed’

Description:

If the Nios II processor’s CPU. Data_master port is not connected to all program memories (memories to which the. Elf file is the downloaded) the software project fails to run on Nios II hardware.

Failure to connect cpu.data_master to all program memories is a design error that the Nios II SBT does not detect.

Workaround/Fix: Connect CPU. Data_master to all program memories.

2. Another question, does systemID cause the above problem when 0 is the default?

answer: no effect.

3, in Nios II, Verify failed between address 0xxxx and 0xxxx error:

Verifying 000xxxxx (0%) Verify failed between address 0xxxxxx and 0xxxxxx Leaving target processor paused forums and networks to ask this question is also a common problem for new players, let me just summarize it:

a. The first step is to determine what device is wrong based on the two addresses following the address. In general, most of the errors are in memory. The method is to look for the wrong device based on the address in SOPC or the address in system.h.

b. check whether the hardware welding is normal. Most of the time, some problems are caused by hardware welding. This is mainly for the boards welded by ourselves. Once there are any welding problems in the address data bus, the Verify Failed error will appear.

c. check if componet in sopc is normal. If you are adding your own interface logic, this section checks to see if it is normal or not.

d. check the design in Quartus: check whether the pin lock is correct, must correspond one to one, there must be no one error; Address alignment problem: pin

to 8, 16, 32 bits of external memory, corresponding address the lowest level should be 0, 1, 2. That is, if you use a 16-bit external storage for

, then the lowest bit is ADD[1], and ADD[0] is not used, otherwise. The data bus must be a bidirectional IO port, which is easy to ignore

. If it is SDRAM, you need to calculate and set the phase shift of PLL.

e. Nios IDE to check whether the project design is correct.

many of these questions reflect the timing of SDRAM, but what exactly is the problem?It is estimated that every netizen will encounter different situations. I just hope that I can finally find the answer to the complete question

transfer: https://www.cnblogs.com/hclmcu/archive/2010/07/12/1775855.html

hclmcu user proposed such an error experience:

is my own experience, is. BDF file symbol when using “Generat Pins for symbol Ports” to automatically generate Pins, the generated Pins appear to be connected to the symbol, but in fact there is no, just manually connect Ports to Pins, the problem will be solved.

I do not understand the operation, can not give the answer, can only record here

Read More:

- Keil prompts the stlink download program to prompt error: Flash download failed – target DLL has been cancelled

- [SSL: CERTIFICATE_VERIFY_FAILED] Certificate Verify Failed (_ssl.C:579)

- ssl.SSLError: [SSL: CERTIFICATE_VERIFY_FAILED] certificate verify failed

- Python uses requests to request and reports SSL: CERTIFICATE_VERIFY_FAILED error

- python3 request module https certificate verify failed error

- nginx: [emerg] bind() to 0.0.0.0:443 failed (98: Address already in use)

- Failed to download when creating Vue project, solution

- python:urllib2.URLError urlopen error [SSL: CERTIFICATE_VERIFY_FAILED] certificate verify failed

- Failed to set up listener: socketexception: address already in use

- Eclipse port occupied( java.net.BindException : address already in use: bind) solution

- An error occurred when installing vs2017: failed to verify the signature of the installation program list

- URLError: urlopen error [SSL: CERTIFICATE_VERIFY_FAILED] certificate verify failed (_ssl.c:833)

- After eclipse eclipse eclipse imports the correct project, an error is reported in XML and other files

- Spark login error unable to verify certificate and certificate host name verification failed

- Error running Eclipse: failed to load the JNI shared library

- Error analysis of veeam backup: failed to create NFC download stream

- Hot code replace failed error in eclipse

- Error: Flash download failed – “cortex-m4″“

- Failed to download package files error after re installing Ubuntu

- C language write() function analysis: write failed bad address