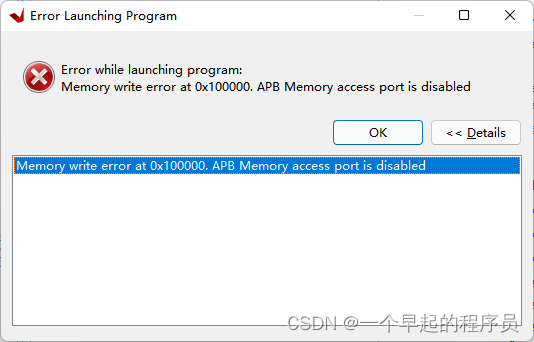

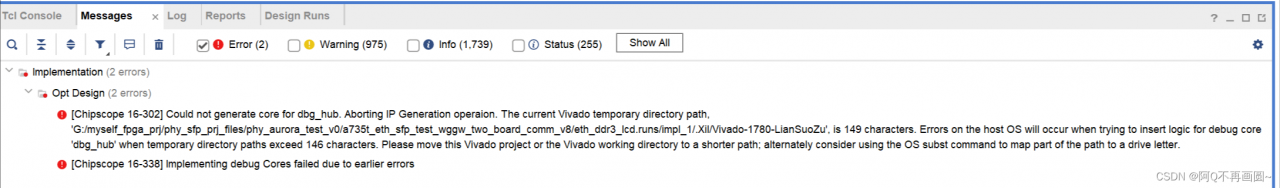

Problem phenomenon

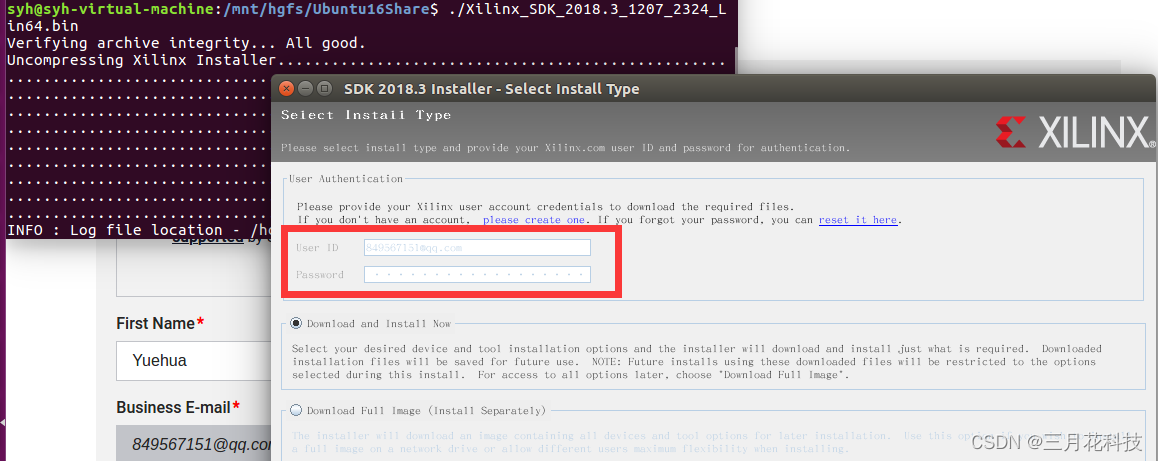

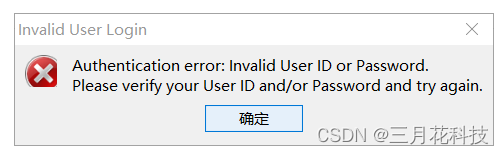

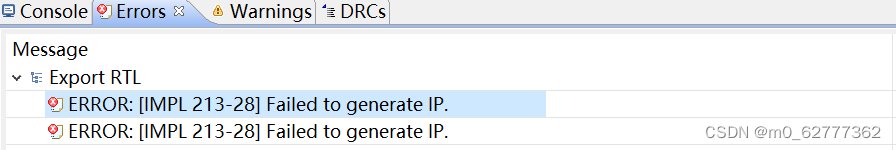

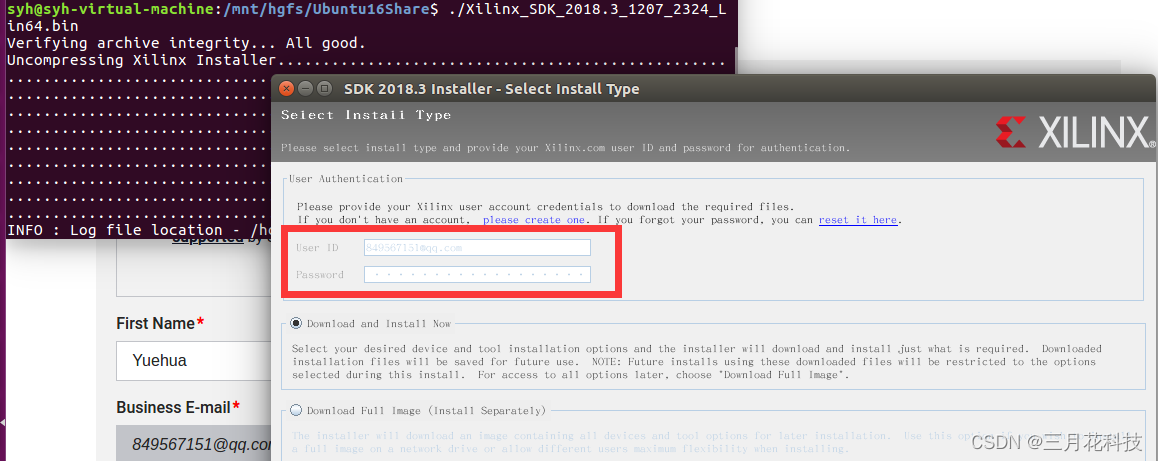

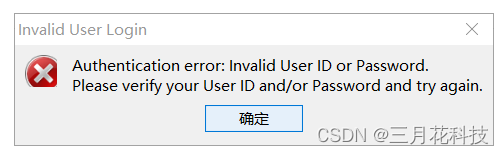

When installing Xilinx_SDK on Linux system, the second step is to enter the Xilinx account name and password, if you don’t have the account name and password, you can click “please create one” in the interface to create one. However, the problem is that after creating the Xilinx user correctly, the software cannot be installed properly, and the error is as follows

The root cause of this problem is that there are still unfilled user information when registering Xilinx accounts. The solution is as follows:

Problem-solving:

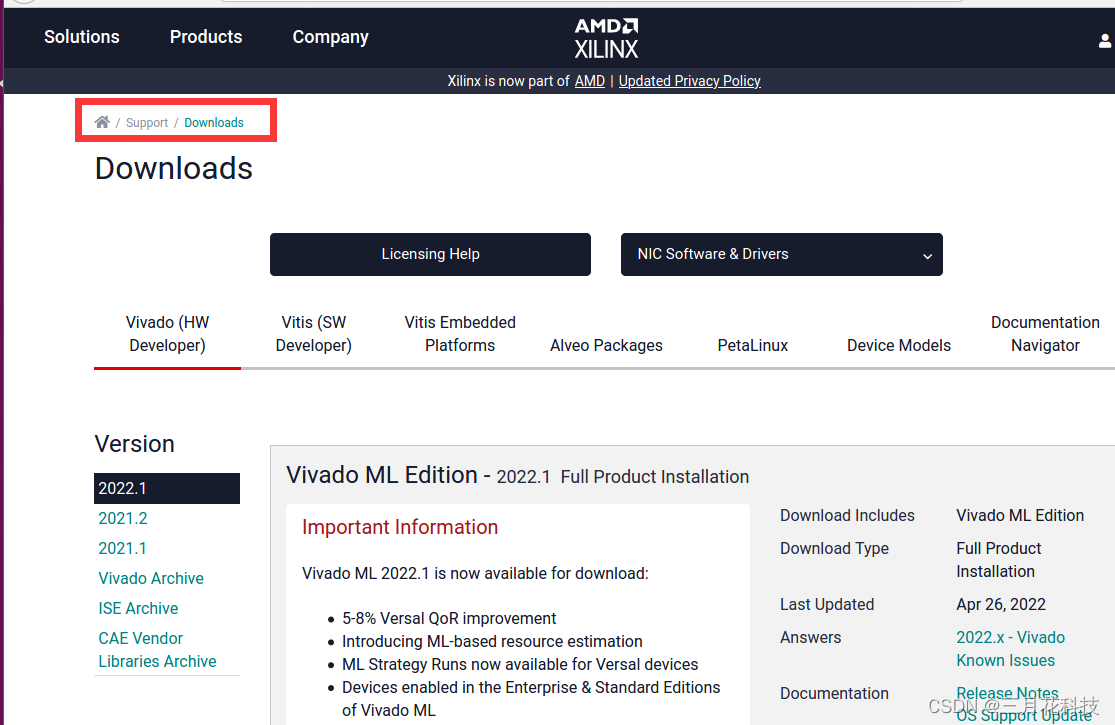

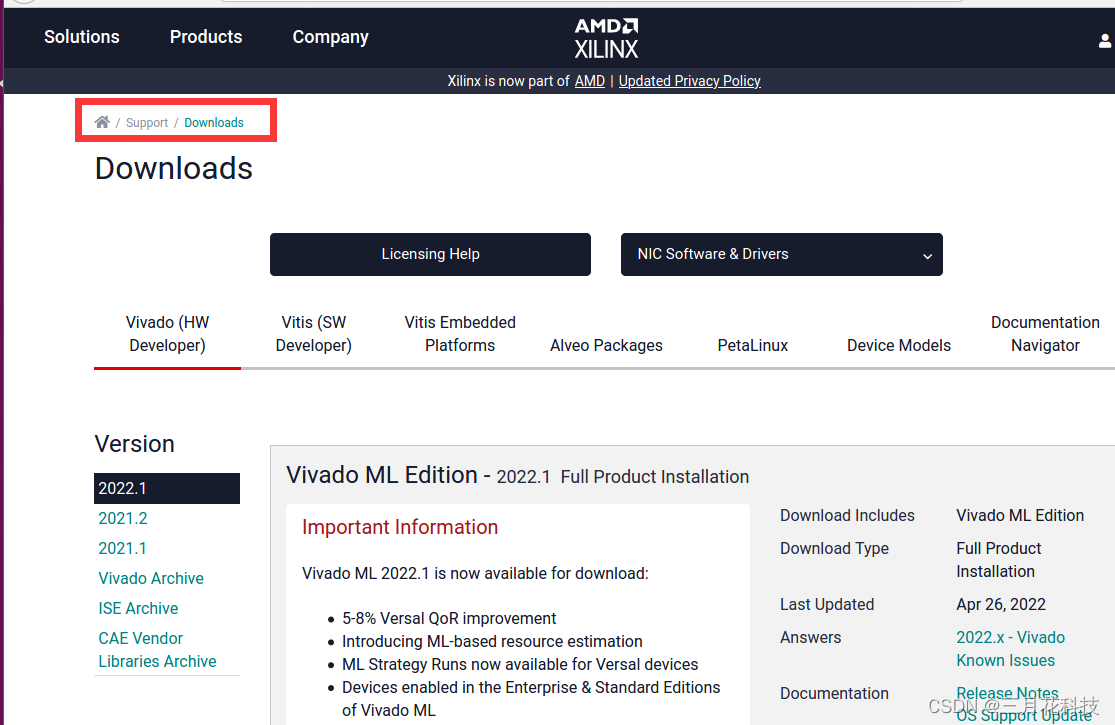

Log in to the official Xilinx website with the registered Xilinx account, and then enter the download station as shown in the following figure:

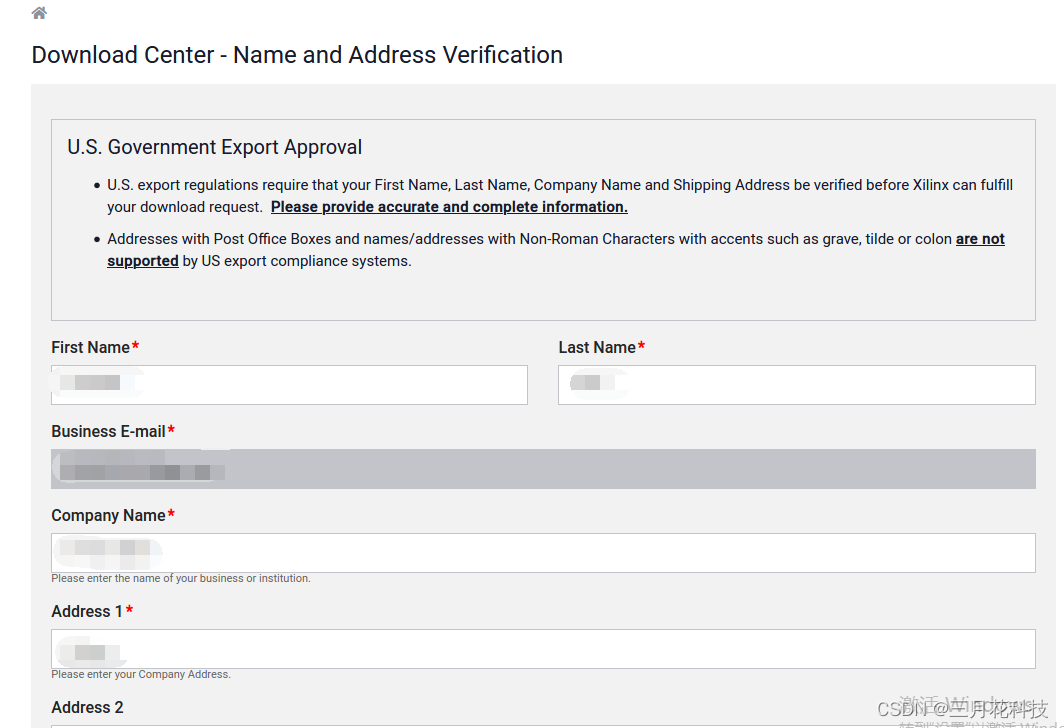

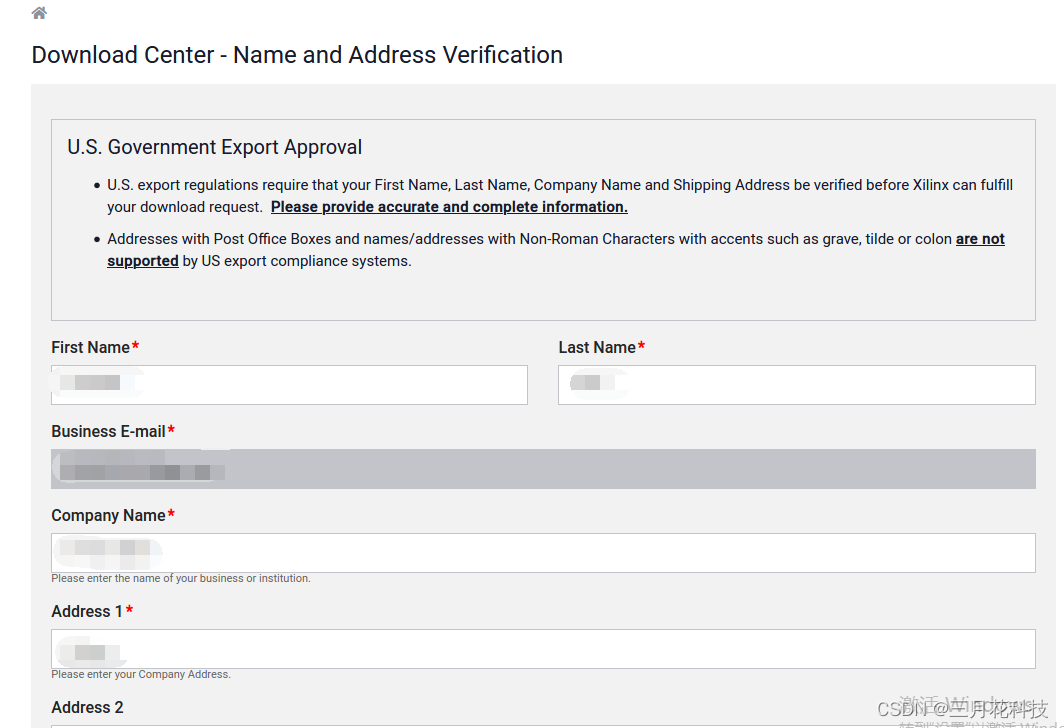

Find something to download. If the account is short of something, you will be prompted to fill in the information. The interface is as follows:

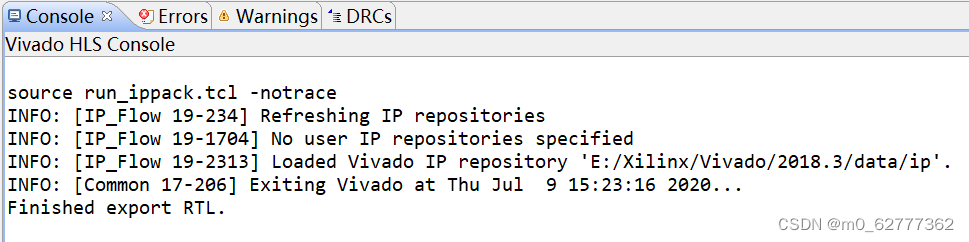

After these information are filled in and submitted, if the selected software can be downloaded normally, it is proved that the personal information missing from Xilinx account is completed.

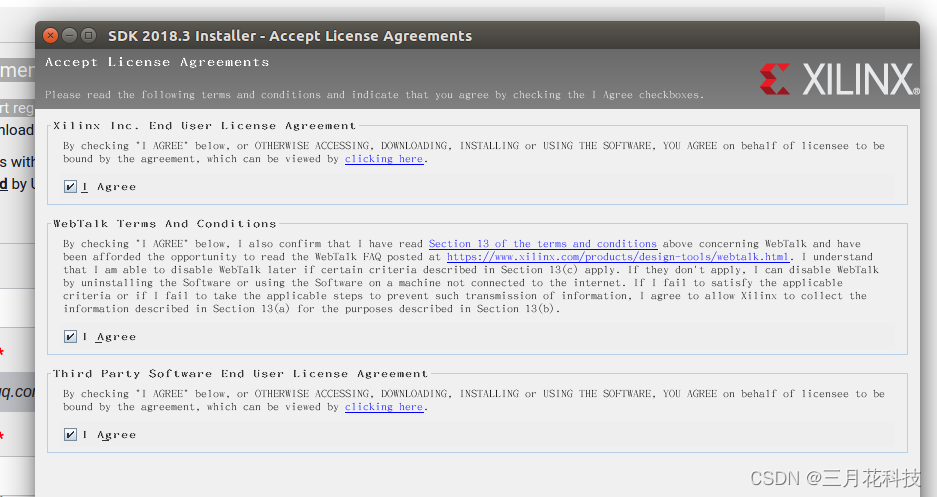

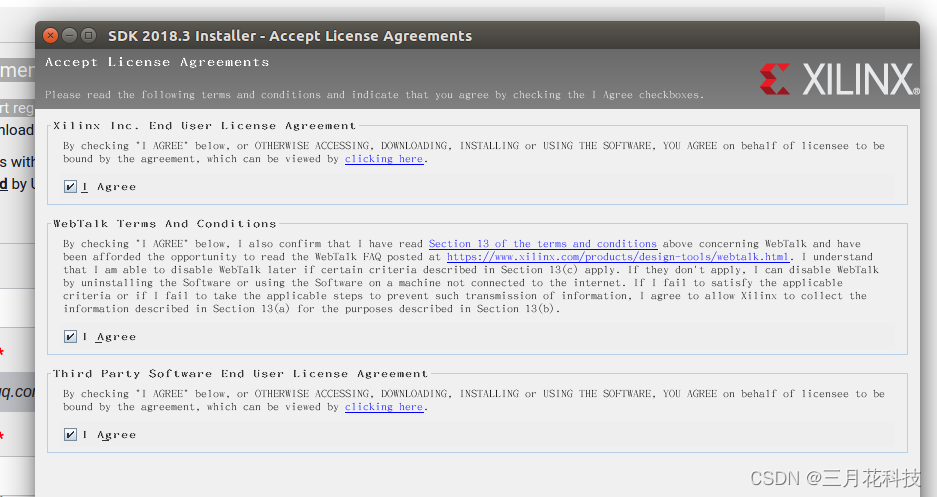

At this point, back to the Xilinx_SDK installation interface, you can use the registered Xilinx account to install normally, and successfully enter the third page of the following figure.

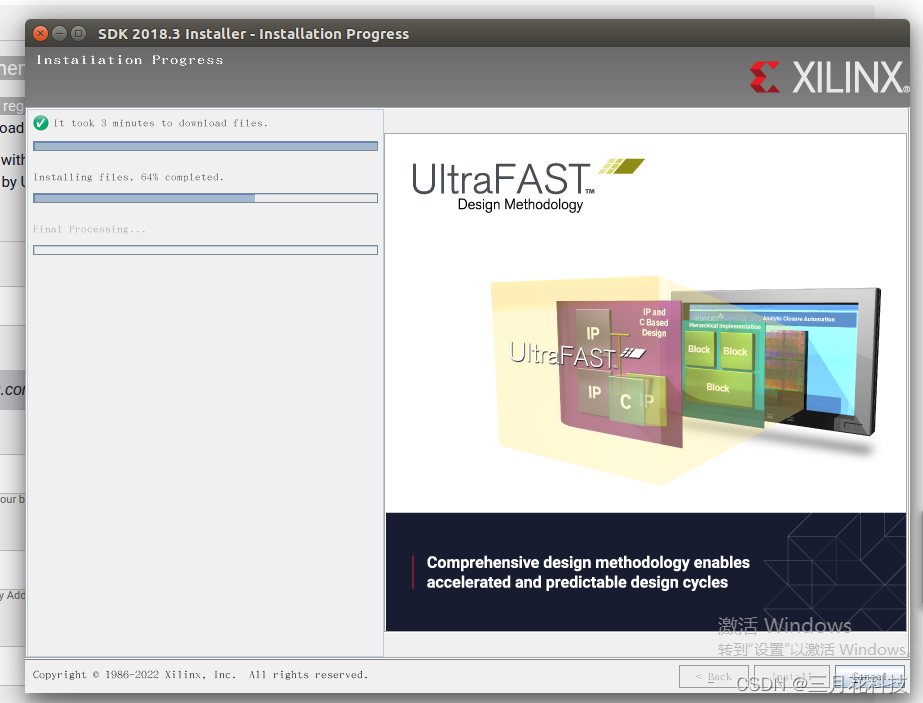

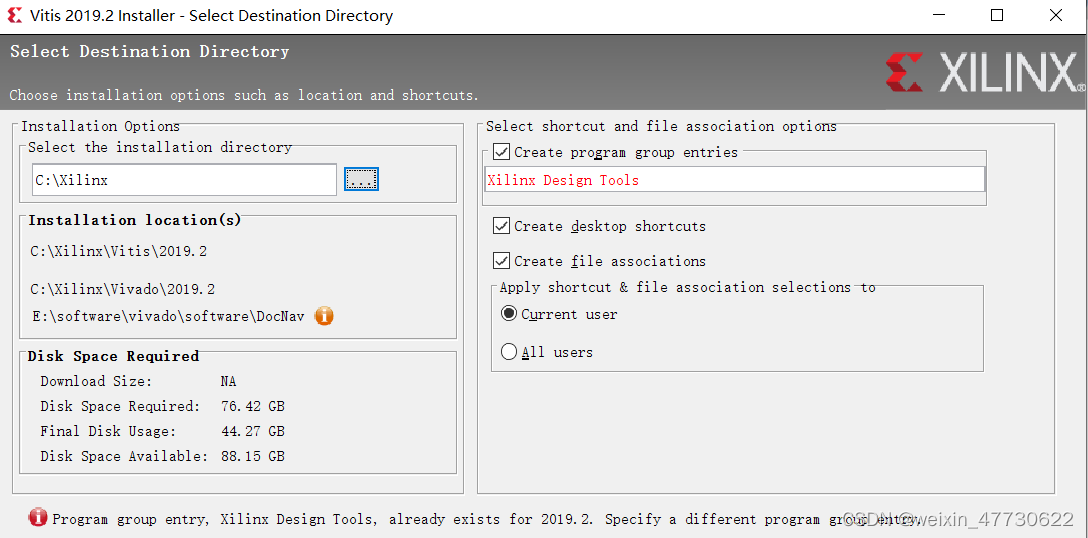

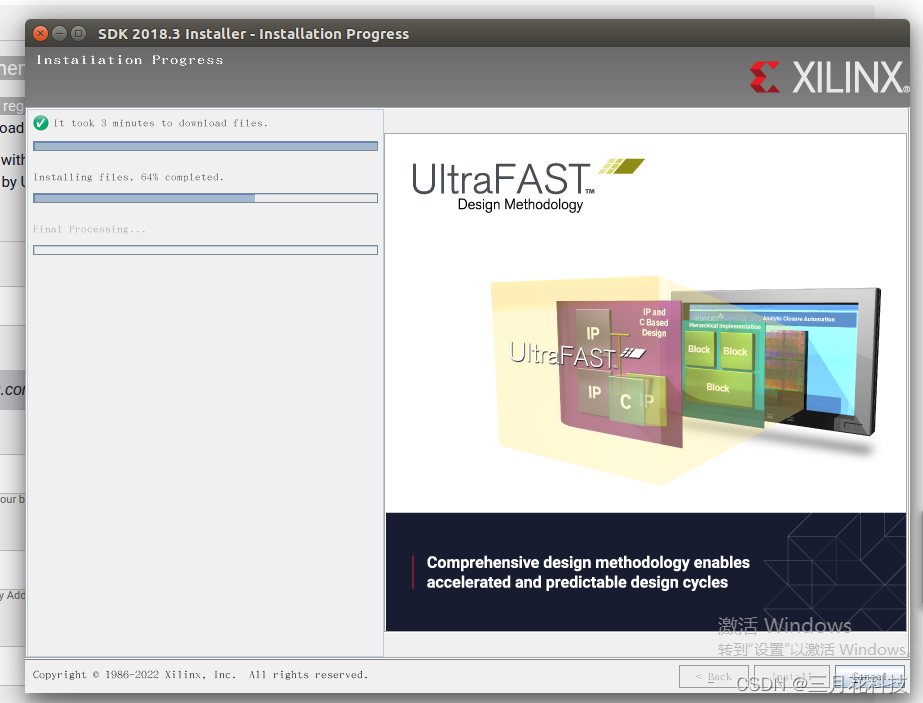

After selecting the content and path to install, you can install normally, as shown in the following figure:

![]()