This article is a summary of my study. If there are copyright or knowledge errors or problems, please contact me directly. Please leave a message

PS: Based on the principle of knowledge sharing, this blog can be reproduced, but please indicate the source!

catalogue

1. Problem description

2. Cause analysis:

3. Problem solving:

1. Problem description

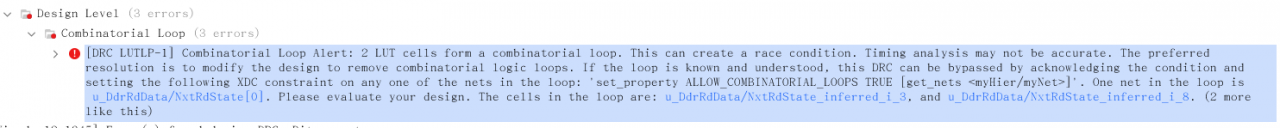

When I debug the project, in order to capture the signal value to observe the timing, I added ILA, and then encountered vivado error when generating bitstream. The warning is as follows:

The specific error contents are as follows:

[DRC LUTLP-1] Combinatorial Loop Alert: 2 LUT cells form a combinatorial loop.

This can create a race condition. Timing analysis may not be accurate. The preferred resolution is to modify the design to remove combinatorial logic loops. If the loop is known and understood, this DRC can be bypassed by acknowledging the condition and setting the following XDC constraint on any one of the nets in the loop: 'set_property ALLOW_COMBINATORIAL_LOOPS TRUE [get_nets <myHier/myNet>]'. One net in the loop is u_DdrRdData/NxtRdState[0]. Please evaluate your design. The cells in the loop are: u_DdrRdData/NxtRdState_inferred_i_3, and u_DdrRdData/NxtRdState_inferred_i_8.2. Cause analysis:

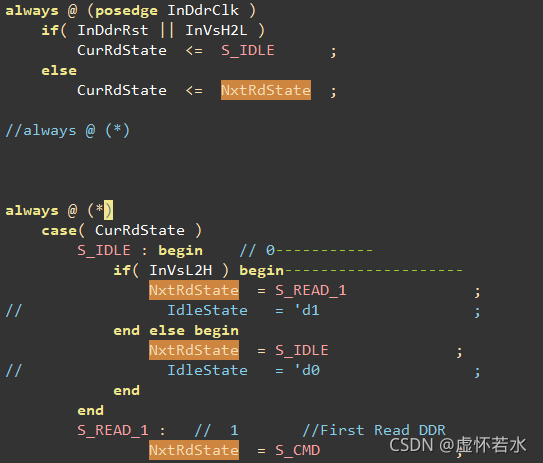

As shown in the code segment below, the combinational loop is combinational logic, which feeds back to itself without registers. The simplest example is an inverter whose output is fed back to the input to produce an oscillator.

Therefore, the combined logic signal nxtrdstate for the state machine cannot be used for ILA grabbing!!!

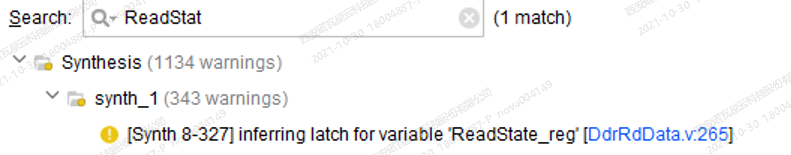

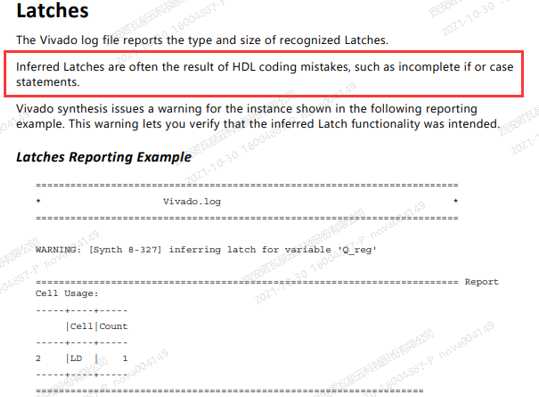

At the same time, the error can be prompted in the warning message of vivado tool:

This warning is described in ug901 as follows:

3. Problem solving:

Do not use ILA to grab the signal value assigned in the combinatorial logic of the state machine!!!