When using quartus to design digital circuits, we encountered the following compilation errors:

Info: *******************************************************************

Info: Running Quartus II 64-Bit Analysis & Synthesis

Info: Version 11.0 Build 157 04/27/2011 SJ Full Version

Info: Processing started: Thu May 15 13:09:59 2014

Info: Command: quartus_ map –read_ settings_ files=on –write_ settings_ files=off simulate -c simulate

Info: Parallel compilation is enabled and will use 2 of the 2 processors detected

Info: Found 1 design units, including 1 entities, in source file simulate.v

Info: Found entity 1: modelsim_ test

Error: Top-level design entity “simulate” is undefined

Error: Quartus II 64-Bit Analysis & Synthesis was unsuccessful. 1 error, 0 warnings

Error: Peak virtual memory: 324 megabytes

Error: Processing ended: Thu May 15 13:10:01 2014

Error: Elapsed time: 00:00:02

Error: Total CPU time (on all processors): 00:00:01

Error: Quartus II Full Compilation was unsuccessful. 3 errors, 0 warnings

as a result of

The module name in Verilog file (. V) is inconsistent with the top-level design entity (usually the file name of. V file).

module modelsim_test(clk,rst_n,div);

input clk;

input rst_n;

output div;

reg div;

always@(posedge clk or negedge rst_n)

if(!rst_n)div<=1'b0;

else div<=~div;

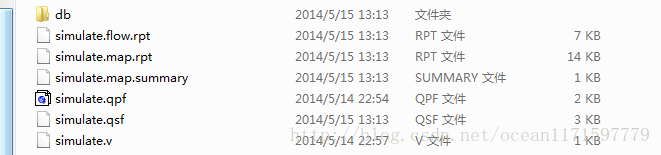

endmodule The name of the module above is Modelsim_ Test, and the Verilog file name in the project directory is simulate, as shown in the following figure.

The solution is: model sim_ Test is changed to simulate.

Compiled successfully!

Read More:

- Top background execution: Top: failed TTY get error

- Eclipse Syntax error, annotations are only available if source level is 1.5 or greater

- Ant Design ‘cross env’ is not an internal or external command, nor is it an error reporting problem for a runnable program

- Error in DESeqDataSet(se, design = design, ignoreRank) : some values in assay are negative

- How to uninstall the software for apple / Mac? What if the software can’t be unloaded?

- Syntax error, annotations are only available if source level is 1.5 or greater.

- JetBrains compilation error is due to project language level

- JetBrains compilation error is due to project language level

- modelsim actually error loading design?

- When opencv is used, vs is stuck and other software works normally

- Eclipse .java File Syntax error, parameterized types are only available if source level is 1.5 or

- ** exception error: undefined function appmon:start/0

- Error (12153): Can‘t elaborate top-level user hierarchy

- “Syntax error, annotations are only available if source level is 1.5 or greater”

- The software licensing service reported that the product SKU is not found

- Syntax error, annotations are only available if source level is 1.5 or greater

- Error in created hook: “referenceerror:” promise “undefined” Vue cli project Google is right, ie reported an error, “promise” undefined“

- How to Fix error performing isolated work; SQL [n/a]; nested exception is org.hibernate.exception.SQLGrammarE

- Java project cannot import entity class package and service package, controller layer reports error, fix project setup is OK

- Keil :error: identifier “int8_ T “is undefined