SATA3.0 Host Controller IP

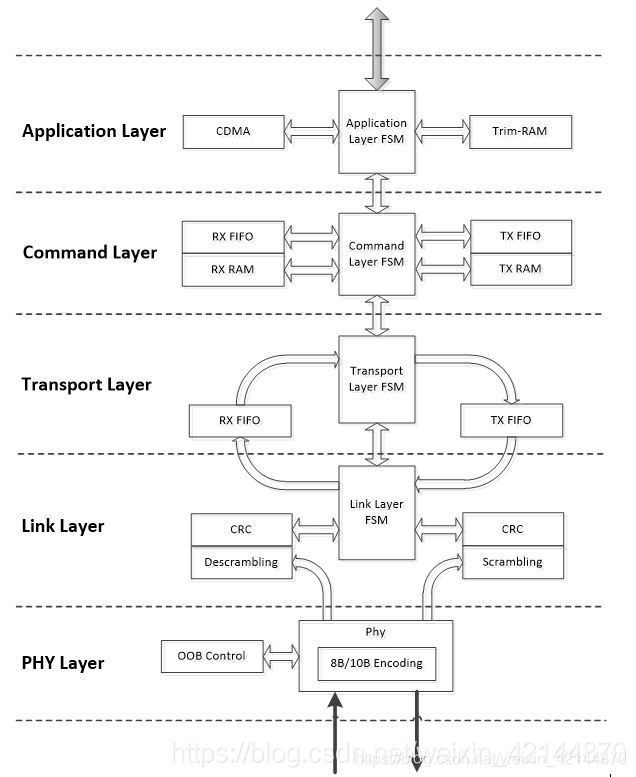

SATA3.0 Host IP not only realizes the PHY (physical layer), LINK (Link layer) and TRN (transport layer) of SATA protocol, but also realizes the CMD (command layer) and APP (application layer), and supports 1.5, 3 and 6Gbps transmission rates, which is fully compatible with SATA specification.

SATA3.0 Host IP provides an efficient and easy to use interface for users to use SATA storage devices. Without user intervention, SATA3.0 Host IP automatically connects, diagnoses, identifies and initializes SATA storage devices, and outputs the Identify Data Structure of SATA devices. SATA3.0 Host IP built-in DMA controller, users can not only access SATA storage devices through IO interface, but also use DMA interface to efficiently read and write SATA storage devices.

SATA3.0 Host IP is not limited to the number of connected SATA storage devices, that is, the number of connected SATA storage devices is programmable.

Kernel features:

SATA3.0 Host IP not only realizes the PHY (physical layer), LINK (Link layer) and TRN (transport layer) of SATA protocol, but also realizes the CMD (command layer) and APP (application layer), and supports 1.5, 3 and 6Gbps transmission rates, which is fully compatible with SATA specification.

SATA3.0 Host IP provides an efficient and easy to use interface for users to use SATA storage devices. Without user intervention, SATA3.0 Host IP automatically connects, diagnoses, identifies and initializes SATA storage devices, and outputs the Identify Data Structure of SATA devices. SATA3.0 Host IP built-in DMA controller, users can not only access SATA storage devices through IO interface, but also use DMA interface to efficiently read and write SATA storage devices.

SATA3.0 Host IP is not limited to the number of connected SATA storage devices, that is, the number of connected SATA storage devices is programmable.

Kernel features:

- and SATA 1.5 Gbps, 3.0 Gbps and 6.0 Gbps industry specification is fully compatible with the AXI – Lite or application registers (ARI) interface, at the same time support IO (including PIO and Trim) and IO DMA operation data interface adopts the design of RAM, the DMA data interface the AXI – Stream or FIFO design support SerDes interface, and the programmable SerDes interface number (the number of SATA storage devices can be connected is programmable, The quantity depends on the number of GT of FPGA) Support SATA storage device with electric plug support Xilinx device: Spartan-6, Virtex-5, Virtex-6, Artix-7, Kintex-7, Virtex-7, Kintex UltraScale, Kintex UltraScale +, Virtex UltraScale +, Virtex UltraScale +, Virtex UltraScale +, Virtex UltraScale +, Virtex UltraScale +, Virtex UltraScale +, Virtex UltraScale +, Virtex UltraScale + for easy integration of synchronous, integrable Verilog design through fully validated SATA3.0 IP

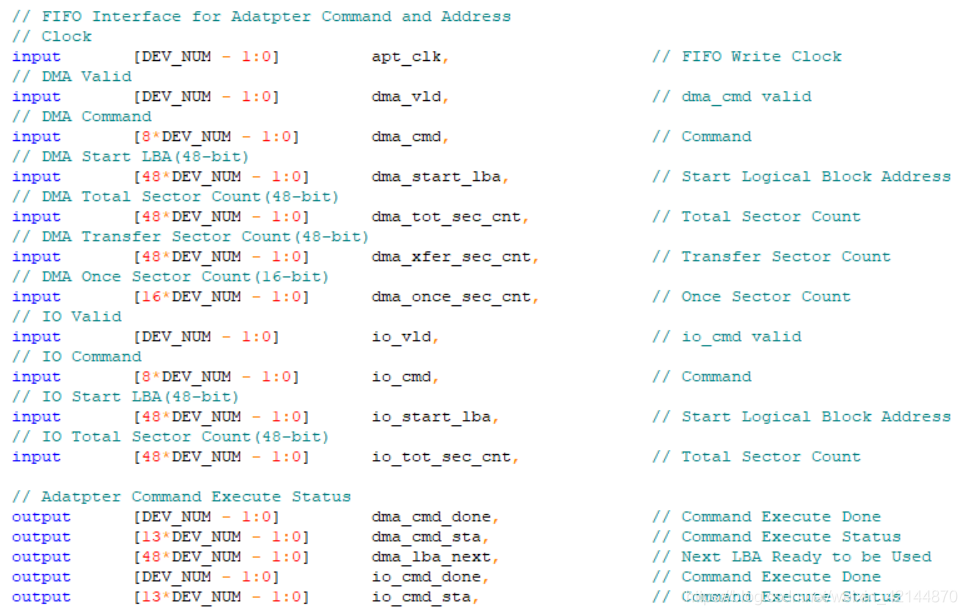

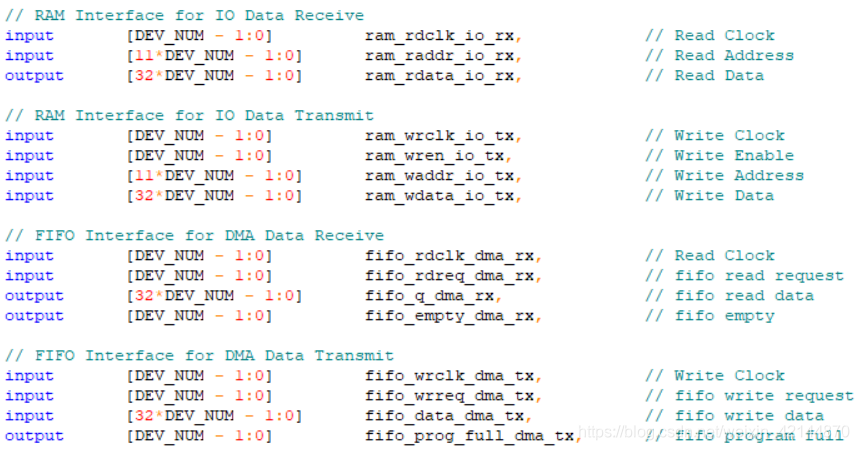

External interface:

- axi-lite or application register (ARI) interface axi-stream or FIFO streaming data bus RAM block data bus

Performance indicators:

- SATA 3.0 Core: Continuous Write Speed> 530MB/s, Continuous Read Speed> 550MB/sSATA 0 Core: Continuous Write Speed> 240MB/s, Continuous Read Speed> 250MB/s s

1 channel (connect 1 SATA storage device) SATA3.0 IP resource usage (XC7K325 as an example) :

- LTS: 3850, FFS: 4630, BRAM: 16, GT: 1

4 channels (connect 4 SATA storage devices) SATA3.0 IP resource usage (XC7K325 as an example) :

- LTS: 15363, FFS: 18468, BRAM: 64, GT: 4

8 channels (connect 8 SATA storage devices) SATA3.0 IP resource usage (XC7K325 as an example) :

- LTS: 30763, FFS: 37011, BRAM: 128, GT: 8

Deliverables:

Design File: Post-synthesis EDIF netlist or RTL SourceTiming and layout constraints, Test or Design Example Project Technical support: email, phone, on-site, training service

Contact Information:

Email:[email protected]

SATA3.0 Host IP Block Diagram