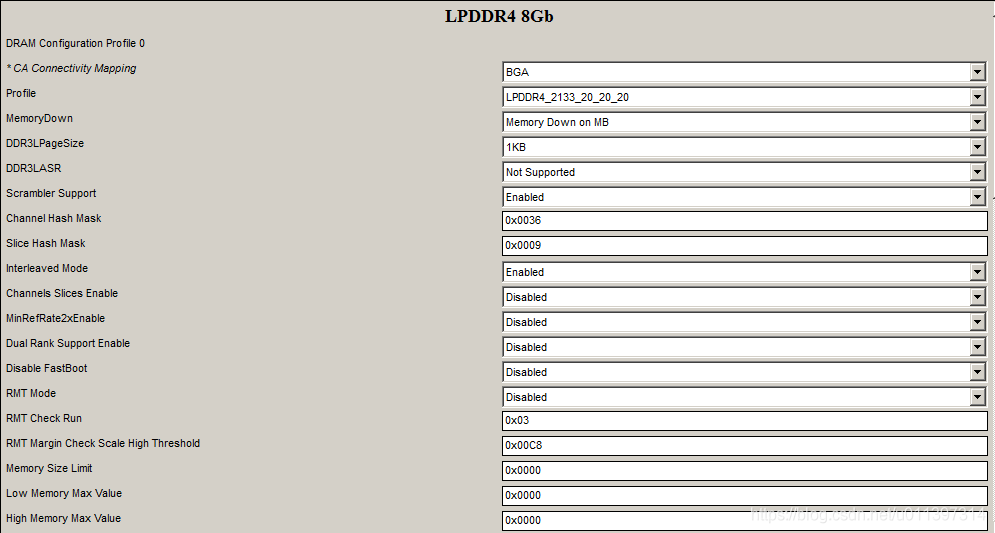

At present, there are two kinds of SMIP and SPD, and now SMIP, soft: BMP, SMIP and SMIP are mainly configured. Relevant document SMIP.c that needs to be modified

BGA: SMT, Dimm: slot, MemoryDown: SMT must be used:

ch0 RankEnable–> Ch0 options, these options are configured according to Memory Spec and Gen, where Ch0_RankEnable:only for Memorydown relates to CS and channel

RMT mode runs edge check mode, which is likely to be a circuit problem if there is a problem. This function is opened for hardware Debug. In the macro definition, the value of Set is unchanged, and the value of option is 0 or 1

Additions, deletions and modifications of smip.c :(to be determined)

DQ Mapping for CHO to CH3:

The ch0 and ch2 corresponding to bit0~31 are DQ 8~15,0~7,24~31,16~23

The ch1 and CH3 corresponding to BIT0 ~31 are DQ 0~31

In addition, some basic information about the project.h file is collected in the project.h file. There are many sub-options in the main option in the setup interface, including BIOS vendor, BIOS Version, build time and other relevant information. However, this project.h file is generated after the build.

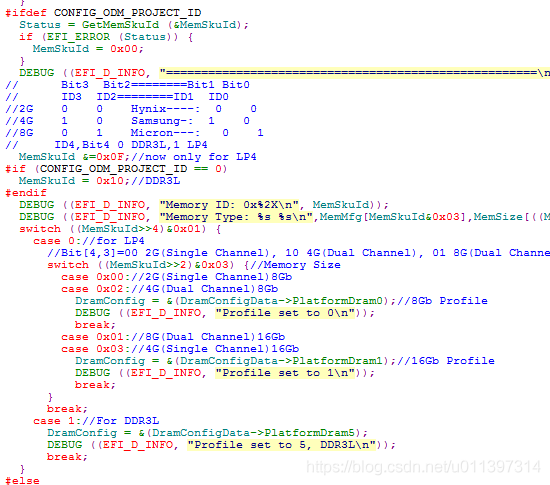

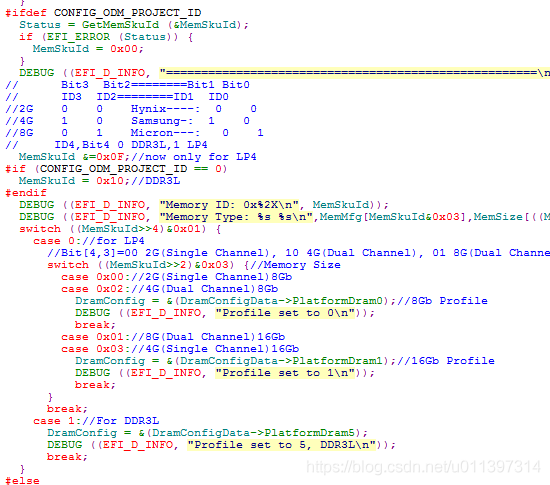

#ifdef CONFIG_ODM_PROJECT_ID

Status = GetMemSkuId (& MemSkuId);

if (EFI_ERROR (Status)) {

MemSkuId = 0x00;

}

DEBUG ((EFI_D_INFO, “=====================================================\n”));

// Bit3 Bit2========Bit1 Bit0

// ID3 ID2========ID1 ID0

//2G 0 0 Hynix—-: 0 0

//4G 1 0 Samsung-: 1 0

//8G 0 1 Micron—: 0 1

// ID4,Bit4 0 DDR3L,1 LP4

MemSkuId & =0x0F; //now only for LP4

#if (CONFIG_ODM_PROJECT_ID == 0)

MemSkuId = 0x10; //DDR3L

#endif

DEBUG ((EFI_D_INFO, “Memory ID: 0x%2X\n”, MemSkuId));

DEBUG ((EFI_D_INFO, “Memory Type: %s %s\n”,MemMfg[MemSkuId&0x03],MemSize[((MemSkuId>>2)&0x03)]));

switch ((MemSkuId> > 4)& 0x01) {

case 0://for LP4

//Bit[4,3]=00 2G(Single Channel), 10 4G(Dual Channel), 01 8G(Dual Channel),11 4G(Single Channel)

switch ((MemSkuId> > 2)& 0x03) {//Memory Size

case 0x00://2G(Single Channel)8Gb

case 0x02://4G(Dual Channel)8Gb

DramConfig = & (DramConfigData-> PlatformDram0); //8Gb Profile

DEBUG ((EFI_D_INFO, “Profile set to 0\n”));

break;

case 0x01://8G(Dual Channel)16Gb

case 0x03://4G(Single Channel)16Gb

DramConfig = & (DramConfigData-> PlatformDram1); //16Gb Profile

DEBUG ((EFI_D_INFO, “Profile set to 1\n”));

break;

}

break;

case 1://For DDR3L

DramConfig = & (DramConfigData-> PlatformDram5);

DEBUG ((EFI_D_INFO, “Profile set to 5, DDR3L\n”));

break;

}

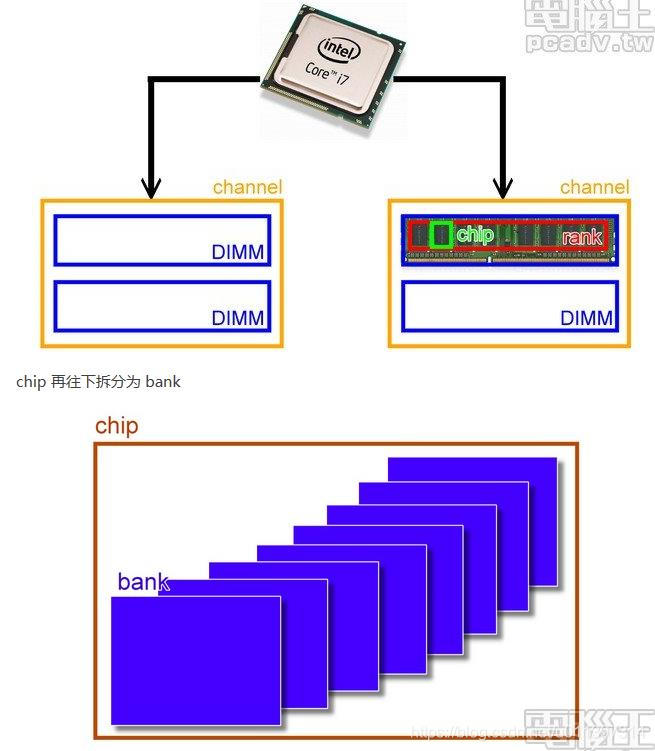

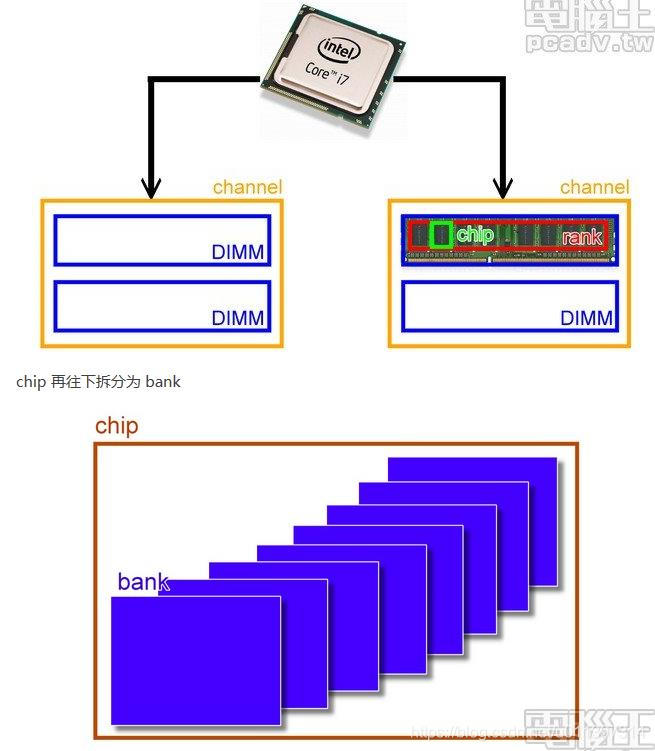

The connections among channel, DIMM,rank, bank, CS and chip in Memory:

A channel corresponds to a set of memory controllers

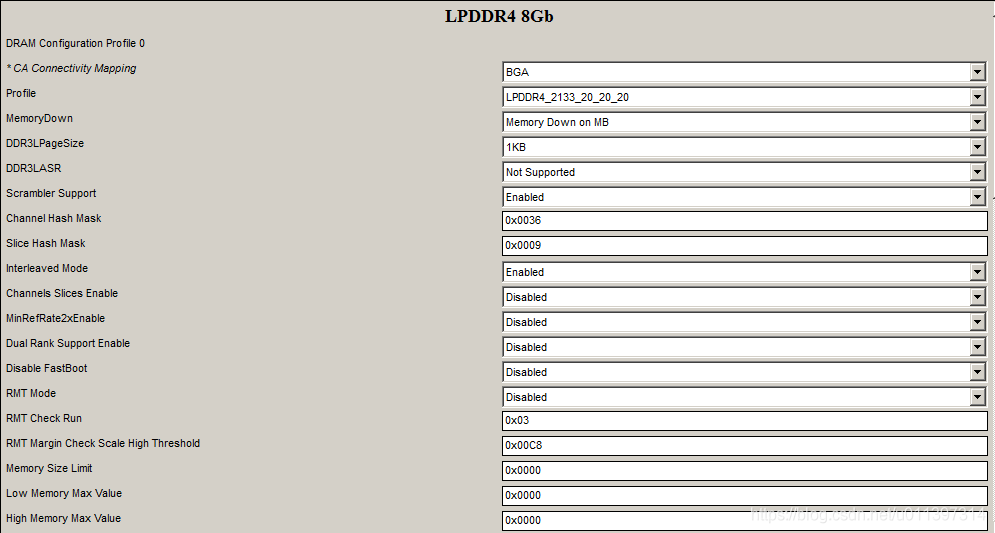

BGA: SMT, Dimm: slot, MemoryDown: SMT must be used:

ch0 RankEnable–> Ch0 options, these options are configured according to Memory Spec and Gen, where Ch0_RankEnable:only for Memorydown relates to CS and channel

RMT mode runs edge check mode, which is likely to be a circuit problem if there is a problem. This function is opened for hardware Debug. In the macro definition, the value of Set is unchanged, and the value of option is 0 or 1

Additions, deletions and modifications of smip.c :(to be determined)

DQ Mapping for CHO to CH3:

The ch0 and ch2 corresponding to bit0~31 are DQ 8~15,0~7,24~31,16~23

The ch1 and CH3 corresponding to BIT0 ~31 are DQ 0~31

In addition, some basic information about the project.h file is collected in the project.h file. There are many sub-options in the main option in the setup interface, including BIOS vendor, BIOS Version, build time and other relevant information. However, this project.h file is generated after the build.

#ifdef CONFIG_ODM_PROJECT_ID

Status = GetMemSkuId (& MemSkuId);

if (EFI_ERROR (Status)) {

MemSkuId = 0x00;

}

DEBUG ((EFI_D_INFO, “=====================================================\n”));

// Bit3 Bit2========Bit1 Bit0

// ID3 ID2========ID1 ID0

//2G 0 0 Hynix—-: 0 0

//4G 1 0 Samsung-: 1 0

//8G 0 1 Micron—: 0 1

// ID4,Bit4 0 DDR3L,1 LP4

MemSkuId & =0x0F; //now only for LP4

#if (CONFIG_ODM_PROJECT_ID == 0)

MemSkuId = 0x10; //DDR3L

#endif

DEBUG ((EFI_D_INFO, “Memory ID: 0x%2X\n”, MemSkuId));

DEBUG ((EFI_D_INFO, “Memory Type: %s %s\n”,MemMfg[MemSkuId&0x03],MemSize[((MemSkuId>>2)&0x03)]));

switch ((MemSkuId> > 4)& 0x01) {

case 0://for LP4

//Bit[4,3]=00 2G(Single Channel), 10 4G(Dual Channel), 01 8G(Dual Channel),11 4G(Single Channel)

switch ((MemSkuId> > 2)& 0x03) {//Memory Size

case 0x00://2G(Single Channel)8Gb

case 0x02://4G(Dual Channel)8Gb

DramConfig = & (DramConfigData-> PlatformDram0); //8Gb Profile

DEBUG ((EFI_D_INFO, “Profile set to 0\n”));

break;

case 0x01://8G(Dual Channel)16Gb

case 0x03://4G(Single Channel)16Gb

DramConfig = & (DramConfigData-> PlatformDram1); //16Gb Profile

DEBUG ((EFI_D_INFO, “Profile set to 1\n”));

break;

}

break;

case 1://For DDR3L

DramConfig = & (DramConfigData-> PlatformDram5);

DEBUG ((EFI_D_INFO, “Profile set to 5, DDR3L\n”));

break;

}

The connections among channel, DIMM,rank, bank, CS and chip in Memory:

A channel corresponds to a set of memory controllers