When using quartus to design digital circuits, we encountered the following compilation errors:

Info: *******************************************************************

Info: Running Quartus II 64-Bit Analysis & Synthesis

Info: Version 11.0 Build 157 04/27/2011 SJ Full Version

Info: Processing started: Thu May 15 13:09:59 2014

Info: Command: quartus_ map –read_ settings_ files=on –write_ settings_ files=off simulate -c simulate

Info: Parallel compilation is enabled and will use 2 of the 2 processors detected

Info: Found 1 design units, including 1 entities, in source file simulate.v

Info: Found entity 1: modelsim_ test

Error: Top-level design entity “simulate” is undefined

Error: Quartus II 64-Bit Analysis & Synthesis was unsuccessful. 1 error, 0 warnings

Error: Peak virtual memory: 324 megabytes

Error: Processing ended: Thu May 15 13:10:01 2014

Error: Elapsed time: 00:00:02

Error: Total CPU time (on all processors): 00:00:01

Error: Quartus II Full Compilation was unsuccessful. 3 errors, 0 warnings

as a result of

The module name in Verilog file (. V) is inconsistent with the top-level design entity (usually the file name of. V file).

module modelsim_test(clk,rst_n,div);

input clk;

input rst_n;

output div;

reg div;

always@(posedge clk or negedge rst_n)

if(!rst_n)div<=1'b0;

else div<=~div;

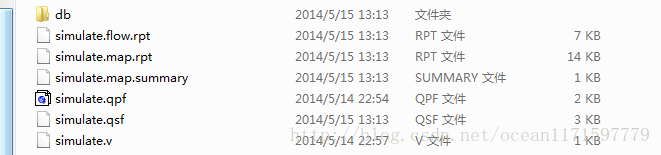

endmodule The name of the module above is Modelsim_ Test, and the Verilog file name in the project directory is simulate, as shown in the following figure.

The solution is: model sim_ Test is changed to simulate.

Compiled successfully!